服務熱線

一、什么是 CoWoP?

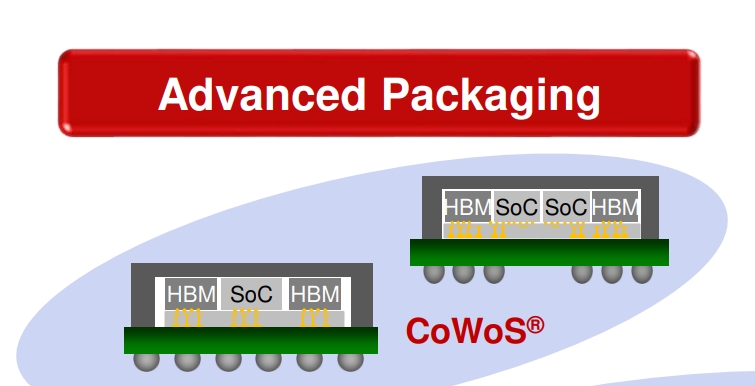

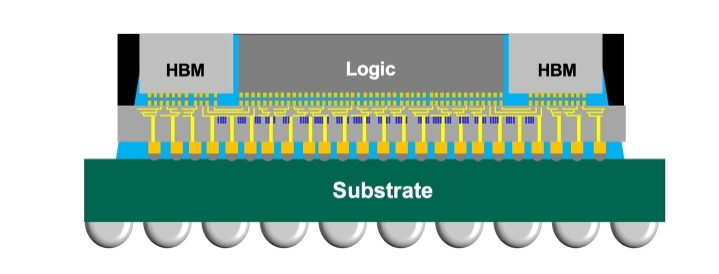

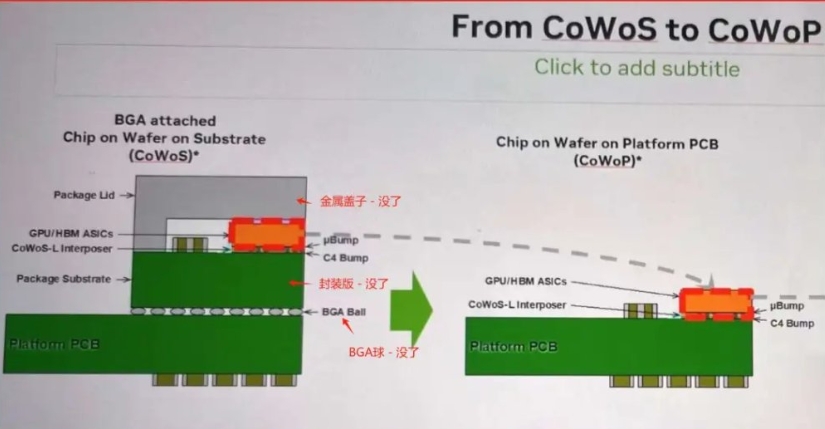

CoWoS(Chip?on?Wafer?on?Substrate):傳統先進的 2.5D 封裝,將硅芯片(Logic + HBM)并排貼在一個中介層(硅 Interposer)上,再焊接到封裝基板(Package Substrate),然后用 BGA 焊球連接到主板。

CoWoP 的核心思路就是把這個封裝基板去掉 —— CoWoP = CoWoS - 封裝基板。中介硅片 + 芯片直接安裝在增強型主板上,不再走傳統封裝那一層。

二、為什么這么做?CoWoP 有什么好處

省掉中間層,降低信號損耗

封裝基板那層走線、引線、接觸都會帶來寄生電阻、電容。去掉后,邏輯芯片對高帶寬連接(如 NVLink)更可靠、更遠、更快。熱性能更強

沒有封裝基板那塊厚材料,封裝熱膨脹系數配合更一致、熱堆棧更薄,散熱更直接、更好控溫,減少板變形(warpage)。成本下降

去掉封裝底板和封裝蓋,少了材料、工藝、BGA焊球等制造步驟,潛在節約封裝成本,同時也減輕整體厚度、體積。

三、CoWoP 的關鍵技術要點

主板(Platform PCB)必須升級

PCB 上要具備過去由封裝 substrate 提供的高密度布線能力,包括精準微線距、精準信號/電源/地層布線能力。中介層(Interposer)依然重要

包含 GPU 核心和 HBM 等小 die,放在高精度硅片 interposer 上,保持高帶寬連接能力。可靠力學與熱匹配設計

硅 interposer、die 與 PCB 的熱膨脹系數(CTE)必須匹配,避免因熱循環導致 warpage 或失效。信號電氣完整性管理

PCB 與 interposer 對高速信號(如 NVLink、HBM RDL)路徑需要嚴格控制阻抗、延遲、電容、電感分布。

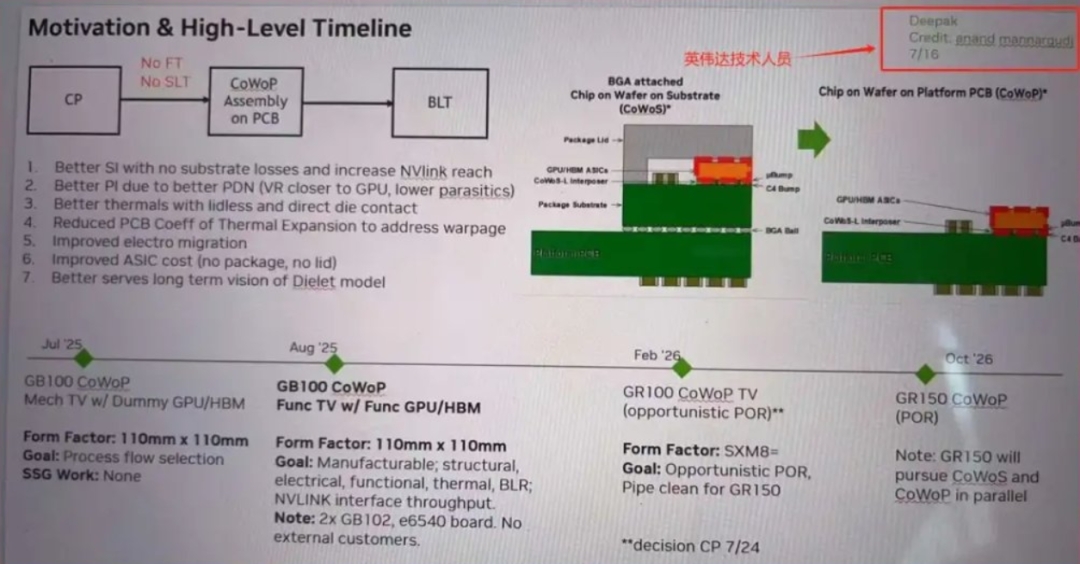

四、NVIDIA 的 CoWoP 規劃與時間節點

自 2025 年 7 月 起,NVIDIA 在內部進行 GB100 的 CoWoP 機械樣板測試(含 Dummy GPU/HBM),尺寸約 110?mm × 110?mm。

2025 年 8 月 將進行結構、電氣、熱性能和 NVLink 帶寬驗證。

2026 年 2 月 開啟 GR100 CoWoP 功能驗證,接著在 2026 年 10 月 推出 GR150 助力并行 CoWoS 與 CoWoP 路線。

五、系統流程概覽(從傳統到 CoWoP)

CoWoP 是在先進 AI 封裝中,去掉了封裝基板這一層,把 die + interposer 直接貼到平臺 PCB 上,借力 PCB 本身承接 substrate 功能,讓信號更快、熱阻更小、成本更低,但要求 PCB、設計和熱機械一體化的集成度非常高。

六、 CoWoP(Chip?on?Wafer?on?Platform) 對半導體產業鏈的影響:

1、封裝模式變革:需求遷移與供應鏈重構

從 CoWoS?S 向 CoWoS?L 或 CoWoP 的轉變,意味著對封裝基板層的大幅調整。NVIDIA 正逐漸減少 CoWoS?S 訂單,集中資源投入 CoWoS?L 與 CoWoP,以支撐 Blackwell 系列高性能 AI GPU 的發展 。

TSMC 的 CoWoS 能力長期供不應求,CoWoP 的推廣可能部分緩解這一瓶頸,特別是若 CoWoP 能有效替代部分 CoWoS-S 產能需求 。

同時,NVIDIA 開始尋求與 UMC、Intel、Amkor、ASE 等合作伙伴合作,建立多元化的封裝供應鏈,減輕對 TSMC 獨占 CoWoS 的依賴。

2、對封裝、PCB、PCB 材料與制造合作伙伴的挑戰

CoWoP 將封裝 substrate 功能遷移到平臺 PCB,這要求 PCB 廠商升級生產工藝:更細線距、高密度線路、多層電源地層、低熱膨脹系數材料等。

原先制作封裝 substrate 的企業,如 Amkor、ASE、SPIL,在 CoWoP 時代需調整定位,可能轉向更多 interposer 的測試與組裝環節,或擴展業務至高精度 PCB 領域。

3、封裝供應商與功耗相關鏈條的重新布局

傳統 CoWoS substrate 供應商業務可能減少,而 提供硅中介層(interposer)的廠商需求將持續增長。

HBM 高帶寬內存供應商(如 SK Hynix、Samsung)由于 CoWoP 依然使用 HBM,與封裝 interposer 集合,因此對 HBM 的依賴繼續強化,市場需求和價格仍上漲趨勢明顯。

4、研發挑戰與聯盟協同升級

CoWoP 要求 PCB 與 interposer、die 一體設計,信號、電源、熱管理、機械力學需協同工程化實現。這推動 設計工具商、EDA、材料商、PCB 廠商共研新規范。

封裝技術更新加快,CoWoP 與 CoWoS?L、FOPLP(扇出面板級封裝)形成互補和競爭。這對封裝廠商提出更高要求,也創造新的合作空間 。

5、產業鏈整體影響概覽

| GPU 芯片廠商(NVIDIA、AMD) | |

| TSMC / UMC | |

| 封裝廠商(Amkor、ASE、Intel Packaging) | |

| PCB 廠商 / 材料商 | |

| HBM 供應商 | |

| 整體行業生態 |

6、小結一句話

CoWoP 帶來的最核心影響是:將封裝 substrate 的功能重置到主板層,推動 PCB 制造商、設計工具、材料供應商與傳統封裝廠商重新協作,重構 AI 封裝與供應鏈生態。 它不僅可能緩解 CoWoS 的產能瓶頸,還將推動封裝與板級供應鏈邁向更高集成度和設計協同性時代。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

粵公網安備44030002007346號

粵公網安備44030002007346號